محاسبه ی ترابرد الکتریکی و اسپین ترونیک

امروزه استفاده از قطعات CMOS (نمیرسانا اکسید فلزی مکمل) در ابزارهای الکترونیکی امری کاملا متعارف است. پیشرفت CMOS اساسا متمرکز برکوچک سازی است به طوری که تعداد ترانزیستورهای مدارهای مجتمع هردو سال تقریبا دو برابر می شود ( این روند به قانون مور معروف است). قطعات CMOS سرانجام به یک محدودیت فیزیکی دچار می گردند به این معنا که کوچک سازی بیشتر اساسا غیر ممکن خواهد بود.

به طور خاص یک نامزد امیدوار کننده برای این جایگزینی اسپین ترونیک است و این به دلیل انطباق آن با فن آوری کنونی است. اسپین ترونیک ظهور یک نظم و انضباط جدید است که هدف آن انقلاب در زمینه فناوری اطلاعات با استفاده از اسپین است، به گونه ای که اطلاعات توسط اسپین انتقال یابد. یکی از ابزارهای مطالعه و طراحی مواد مناسب جهت کاربرد در اسپین ترونیک، رهیافت تئوری تابعی چگالی (DFT) می باشد که در سالهای اخیر مورد توجه محققین قرار گرفته است:

پروژه های دکتری و کارشناسی ارشد متعددی در رشته ی مهندسی برق الکترونیک (بخصوص دانشگاه خواجه نصیرالدین طوسی) و رشته ی فیزیک جهت بررسی نانوساختارها برای کاربرد در اسپین ترونیک زمینه تعریف می شوند، همچنین دانشجویان شیمی و مهندسی مواد نیز جهت کاربردهای سنسوری و حسگری می توانند این گونه پروژه ها را برای پایانامه های خود تعریف کنند.

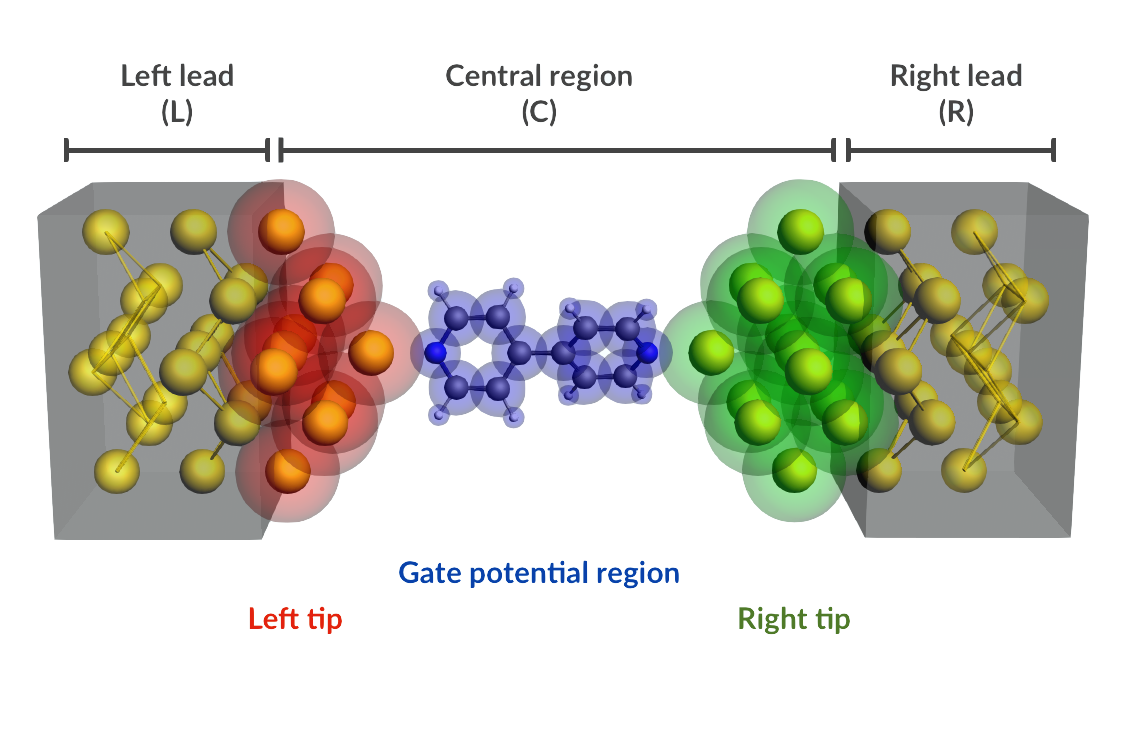

از مهمترین نرم افزارهایی که در این زمینه از آنها بهره برده می شود نرم افزار معروف Siesta و پکیج ترابردی آن به نام TranSiesta می باشد که تا کنون 7 هزار مقاله ی علمی معتبر با این نرم افزار به چاپ رسیده اند.

نمونه مقالاتی که در این حوزه منتشر شده اند:

.

![]()